# Atomic Read-Modify-Write Operations are Unnecessary for Shared-Memory Work Stealing

Umut Acar, Arthur Charguéraud, Stefan Muller, Mike Rainey

## ▶ To cite this version:

Umut Acar, Arthur Charguéraud, Stefan Muller, Mike Rainey. Atomic Read-Modify-Write Operations are Unnecessary for Shared-Memory Work Stealing. [Research Report] 2013. <a href="https://doi.org/10.100/journal.org/">https://doi.org/10.100/journal.org/</a>

HAL Id: hal-00910130

https://hal.inria.fr/hal-00910130

Submitted on 27 Nov 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **Atomic Read-Modify-Write Operations are Unnecessary for Shared-Memory Work Stealing**

Umut A. Acar

Carnegie Mellon University & Inria

umut@cs.cmu.edu

Arthur Charguéraud Inria & LRI, Université Paris Sud, CNRS charguer@inria.fr Stefan Muller

Carnegie Mellon University

smuller@cs.cmu.edu

Mike Rainey

Inria

mike.rainey@inria.fr

#### **Abstract**

We present a work-stealing algorithm for total-store memory architectures, such as Intel's X86, that does not rely on atomic readmodify-write instructions such as compare-and-swap. In our algorithm, processors communicate solely by reading from and writing (non-atomically) into weakly consistent memory. We also show that join resolution, an important problem in scheduling parallel programs, can also be solved without using atomic read-modify-write instructions.

At a high level, our work-stealing algorithm closely resembles traditional work-stealing algorithms, but certain details are more complex. Instead of relying on atomic read-modify-write operations, our algorithm uses a steal protocol that enables processors to perform load balancing by using only two memory cells per processor. The steal protocol permits data races but guarantees correctness by using a time-stamping technique. Proving the correctness of our algorithms is made challenging by weakly consistent shared-memory that permits processors to observe sequentially inconsistent views. We therefore carefully specify our algorithms and prove them correct by considering a costed refinement of the X86-TSO model, a precise characterization of total-store-order architectures.

We show that our algorithms are practical by implementing them as part of a C++ library and performing an experimental evaluation. Our results show that our work-stealing algorithm is competitive with the state-of-the-art implementations even on current architectures where atomic read-modify-write instructions are cheap. Our join resolution algorithm incurs a relatively small overhead compared to an efficient algorithm that uses atomic read-modify-write instructions.

## 1. Introduction

As parallel computing becomes mainstream with the advent of multi- and many-core computers, techniques for writing and executing parallel programs have become increasingly important. By allowing parallel programs to be written at a high level and in a style similar to sequential programs, implicit parallelism, as elegantly exemplified by languages such as Cilk [16], Fork/Join Java [27], NESL [4], parallel Haskell [24], parallel ML [15], TPL [28], and X10 [8], has emerged as a promising technique for parallel programming. Programs written in these implicitly parallel languages generate a plethora of fine-grained parallel threads, requiring an efficient and scalable scheduler for execution. In the course of the last decade, the work-stealing algorithm [6, 7, 16, 17] has proved to be an effective scheduling strategy.

Work stealing can be expressed simply and elegantly at a high level when assuming a sequentially consistent memory model and low-cost synchronization operations such as locks. Each processor maintains a pool of ready threads. When it creates a new parallel thread, the processor adds the thread to its pool. When in need of a thread, it takes one from its pool. If the pool is empty, then the processor steals work from another processor's pool. To guarantee efficiency under a sequentially consistent memory model [6], it suffices 1) to maintain pools as doubly-ended-queues, i.e., *deques*, 2) to choose randomly the processor to steal from, and 3) to steal the "largest" (top) thread from a deque.

In practice, however, synchronization is expensive and can prevent scalability. Furthermore, parallel architectures support only weakly consistent memory models, where certain basic operations such as memory writes are not atomic and making them atomic by use of synchronization operations such as memory fences can be expensive. There has therefore been much research on designing concurrent data structures and algorithms for efficient work stealing on weakly consistent memory. Much of this work focused on

- reducing the use of locks and other atomic read-modify-write operations (e.g., compare-and-swap and fetch-and-add) to improve efficiency and scalability, and

- reducing *memory fences* (e.g., a store-load barrier) so that the benefits of weak memory architectures can be realized without unnecessarily serializing memory operations.

Based on Dijkstra's mutual exclusion protocol, Frigo et al [16] present a work-stealing algorithm that uses locks only when performing steals and only in an edge case of local deque operations. Other papers [2, 9] present non-blocking work-stealing algorithms that use atomic read-modify-write operations instead of locks. Such non-blocking algorithms have been shown to perform well on certain existing hardware such as current multicores. Michael et al [29] show that it can be beneficial to eliminate all memory fences and atomic instructions from local deque operations in total-store or-

der memory models. Their approach, however, weakens the semantics of work stealing by allowing a thread to be removed from a deque (and thus executed) multiple times, which in some cases can also adversely affect correctness and efficiency. More recent work [1] presents a work-stealing algorithm that eliminates all memory fences and atomic instructions from local deque operations on total-store-order memory models without weakening the semantics of work stealing or adversely affecting its performance.

While much progress has been made in reducing the use of atomic read-modify-write instructions and memory fences, the question of whether they can all be eliminated remains open. We find this question to be theoretically interesting, because it hints at the limits of computing with processors that communicate nonatomically via weakly consistent memory. The problem also appears to be of practical interest. In current architectures, atomic instructions are relatively cheap, because they can take advantage of the cache-coherence protocol implemented in hardware. It is not known, however, whether they can scale to computers with larger numbers of processors. For example, citing such concerns, recent work [25, 32] proposes hardware support for work stealing that can improve performance significantly by eliminating certain atomic and synchronization operations. In addition, future parallel hardware may not support at all the cache coherence protocols on which fast implementations of atomic read-modify-write operations rely (e.g., [21]). For example, Intel's SCC (Single Chip Cloud computer) architecture provides for a shared memory architecture but not for cache coherence nor for atomic read-modify-write instructions. Such architectures would require algorithms that do not use atomic read-modify-write instructions.

In their work on work-dealing, Hendler and Shavit also describe techniques that can be used to eliminate all atomic read-modify-write operations [18]. The idea would be to establish pairwise communication channels between processors implemented as producer-consumer buffers without using atomic read-modify-write instructions. To send a message to another, a processor would write to their dedicated channel; to receive a message, it would scan through its channels. Unfortunately, for P processors, this approach would require  $\Theta(P^2)$  communication channels in total, and  $\Theta(P)$  worst-case time for receiving messages. P

In this paper, we present a work-stealing algorithm for weak memory architectures that uses no atomic read-modify-write operations and no memory fences on *total-store order*, *TSO* for short, architectures<sup>2</sup> (Section 4). To ensure efficiency, our algorithm uses only two memory cells per processor and permits data races to take place, recovering from them to guarantee correctness. In addition, we present a *join-resolution* algorithm for fork-join parallel programs for determining when threads become ready without using any atomic read-modify-write operations or memory fences.

We carefully specify our algorithms and prove their correctness and termination properties (Section 5). Since such proofs require reasoning precisely about the memory operations, we consider a specific TSO architecture, Intel's X86, as formalized by the X86-TSO memory model [33]. The X86-TSO model, however, is not sufficient to reason about termination and efficiency. Inspired by the work of Dwork et al. [12] on the partial synchrony model of distributed computing, we therefore present a costed extension of X86-TSO that bounds the time for a memory write to become visible to other processors. We denote this bound  $\Delta$ . Our algorithms

do not assume knowledge of  $\Delta$ . We refer to the costed model as *X86-ATSO*, short for *algorithmic X86-TSO*.

Our correctness proof based on the X86-ATSO model establishes the invariants that our scheduler must observe and shows that they remain true during execution, including as writes performed by a processor become non-deterministically visible to other processors. We don't prove our algorithm to be theoretically efficient—such a proof seems to be another major undertaking (without making strong assumptions). We do, however, briefly describe why we believe that our algorithms satisfy important invariants for efficiency (Section 6) and provide experimental evidence that our algorithms are practical (Section 7).

We show that our algorithms can be implemented without significant difficulty and provide an empirical evaluation by considering a set of benchmarks, including standard Cilk benchmarks as well as more recently proposed graph benchmarks from the PBBS [3] suite (Section 7). For comparison, we use a compare-and-swap-based private-deques algorithm, the traditional Chase-Lev algorithm with concurrent deques [9], and CilkPlus [22]. We expect our algorithms to be especially beneficial in future large-scale systems where atomic read-modify-write operations are expensive or unsupported in hardware. Our experiments show that, even on current architectures, our work-stealing algorithm is competitive with the state of the art and that our join-resolution algorithm has a small but noticeable overhead, suggesting that further work may be needed on that problem.

Due to space constraints, we have included proofs and more detailed experiments in a separately submitted appendix.

## 2. Background and Overview

We briefly present an overview of the main ideas in our algorithms in the context of prior work. We make the ideas precise by presenting detailed specifications of the algorithms in Section 4.

Throughout the paper, we assume fork-join parallelism and restrict ourselves to degree-two joins for simplicity. Since arbitrary-degree joins can be represented with a collection of degree-two joins, this assumption causes no loss of generality.

#### 2.1 Work stealing

**Centralized scheduling.** The simple approach to scheduling is to keep a centralized pool of threads shared by all processors. When a processor creates a new thread, it places the thread into the shared pool. When a processor goes idle, it removes a thread from the pool to run. This algorithm requires the operations on the shared pool to be atomic, making the approach inefficient and unscalable.

Work stealing with atomic read-modify-write operations. For improved efficiency and scalability, work stealing employs multiple pools instead of one and performs load balancing via steals to keep processors busy. More specifically, each processor is assigned a pool implemented as a doubly ended queue (deque). When a processor creates a thread, it pushes the thread into the bottom end of its deque. When it needs a thread, it pops a thread from the bottom. If the deque is empty and thus there is no thread to be popped, the processor attempts to steal a thread from the top end of another process's deque. Progressive advances in the last two decades have reduced the need for atomic instructions dramatically [1, 2, 9, 16, 29]. Existing approaches, however, all rely on atomic insructions to support steals.

Work-stealing without atomic read-modify-write operations. Our starting point is a recent work-stealing algorithm [1] that eliminates all atomic read-modify-write operations and memory fences from local deque operations. The idea behind that algorithm is to use a private-deques architecture for work stealing, where each processor owns a non-concurrent, private deque (instead of a concurrent

<sup>&</sup>lt;sup>1</sup> Using atomic read-modify-write operations,  $\Theta(P)$  time for receiving a message can be reduced to  $O(\log P)$ .

$<sup>^2</sup>$  Architectures that support weaker memory models such as ARM multicore chipsets can often emulate TSO, possibly by using some memory fences, which tend to require local re-ordering of operations performed by one processor.

deque as is traditionally used) and relies on communication to perform load balancing via steals; such communication can be performed via well-understood polling techniques. The algorithm uses atomic read-modify-write operations to support steals.

To see how we can eliminate all atomic operations (without adding memory fences) by building on the private-deques architecture, suppose that we create pairwise communication channels, a total of P(P-1), between each pair of processors. We can use each channel as a pairwise producer-consumer buffer and implement it without using atomic read-modify-write primitives and memory fences [18, 26]. This algorithm would be correct but it has three shortcomings: 1) it requires  $P(P-1) \in \Theta(P^2)$  communication channels, 2) a processor needs  $\Theta(P)$  time for receiving a message, and 3) it violates a key invariant of work stealing: since an idle processor can receive multiple threads, one thread can remain "stuck" in a channel for some time during which it cannot be stolen; this breaks a key efficency invariant of work stealing—that the topmost thread in a deque is stolen first.

To regain efficiency, we reduce the number of channels and limit them so that they can hold only one message at a time. More specifically, instead of using P pairwise communication channels, in our algorithm, each processor owns just two cells: one *query* cell for receiving incoming steal queries and one *transfer* cell for receiving the threads sent to it; each cell can hold only one query or transfer object. When a processor wishes to steal from another target processor, it sends a message to the target processor by non-atomically writing to its query cell and waits for a response. When a processor receives a steal query, it sends the thread at the top of its deque by writing to the transfer cell of the querying processor; if the processor has no threads then it denies the request again by writing to the transfer cell of the querying processor.

This approach leads to at least two issues: 1) since the query is made non-atomically, a query can be overwritten by another processor's query in a data race, and 2) since all communication takes place via non-atomic write operations and no memory fences can be used, writes can be delayed arbitrarily, causing inconsistenciens. To solve these problems, our algorithm keeps a logical clock at each processor, counting uninterrupted rounds of work. Each round starts when a processor gets work, or satisfies (by sending work) a steal query, or declines (because it has no work to share) the steal query. To solve the first problem—the problem of steal queries overwritten in a data race—we use the logical clocks, called round *numbers*, as follows: when an idle processor a sends a steal query to a target processor b, it tags its query with the round number of b. When a's query is overwritten by the query of another processor c, b cannot see a's request but will eventually respond to c (or another processor) and increment its round number. Processor a can detect that its steal attempt has failed by observing that the round number of b has increased. The second problem—the problem of delayed writes— can cause the query of an idle processor to be overwritten by another query, which was made at an earlier round. The idle processor detects such an inconsistent write by observing the round number of the query cell of the target, and rewriting its query as needed.

#### 2.2 Join Resolution

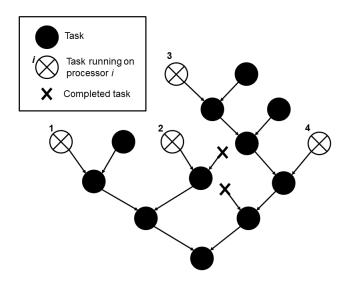

For work-stealing to be efficient, it is important for a thread to be made available for execution as soon as it becomes ready, i.e., all its ancestor threads are executed. Threads with a single parent are ready when created but *join threads* with two parents become ready only when both parents complete execution. Since parents can be executed by different processors, determining when join threads become ready can involve coordination between processors.

Join resolution with atomic read-modify-write operations. It is relatively straightforward to give a simple algorithm for join reso-

lution when using atomic read-modify-write instructions. For example, each join thread can keep a counter of unfinished parent threads. The counter initially contains the number of parents and is atomically decremented by the processor that executes a parent. The join thread is ready when the counter reaches zero. This algorithm can be optimized to use atomic instructions only for nonlocal joins that involve two processors [16]. With this optimization, experimental evidence suggests that join resolution works efficiently on some modern parallel systems, because non-local joins are rare (one per steal) and only two processors contend for the same memory object. This optimization has been used in Cilk [16] as well as our own comparison implementations. Another approach to join resolution would be to keep a two-processor barrier. This approach has the disadvantage of holding up the processor that first completes a parent, breaking a crucial greedy property of work stealing.

Join resolution without atomic read-modify-write operations. To develop some intuition for the problem, we start by assuming that every memory write becomes visible to all processors in some known time  $\Delta$  and that we know the two processors that will execute the parents of the join thread. We create pairwise communication channels between all processors and send and receive messages through them without using atomic instructions [18, 26]. Now, when processor i finishes a parent thread, it sends a READY message to the other processor j working on the other parent, which we know by assumption, and waits for a response for  $2\Delta$  time units. If j receives this message before it completes the parent thread, then it will execute the join thread. If, however, j finishes before hearing from i, then it sends READY to i, causing both processors to receive READY, indicating a tie, which can be broken arbitrarily. If i has not received READY from j after  $2\Delta$  units of time, processor i continues to obtain other work.

We now describe how to eliminate three strong assumptions made by this algorithm: 1) synchronous communication, 2) knowledge of the processors executing the parents, 3)  $\Theta(P^2)$  buffers. We avoid using  $\Delta$  by requiring each processor to acknowledge the receipt of a READY message by sending an ACK message back. Thus, after sending READY, a processor will wait until it eventually gets back either READY, indicating a tie, or ACK, indicating success, and may proceed accordingly in either case.

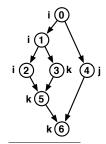

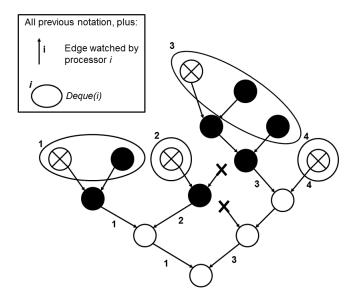

For the second problem, note it is impossible to know the processors participating in a join *a priori*. Figure 1 illustrates an example, where processor i starts to execute thread 0, which creates thread 1 and thread 4, which is then stolen by processor j. At this time, our only knowledge for thread 6, the join thread of 1 and 4, is that it might be decided between the processors i and j. When 1 executes, however, it forks the threads 2 and 3, which is stolen by processor k. Thus, the processor that executes the join thread of 2 and 3, either i or k, will actually participate in the resolution of thread 6 but there is no way to know which—the outcome will be non-deterministic.

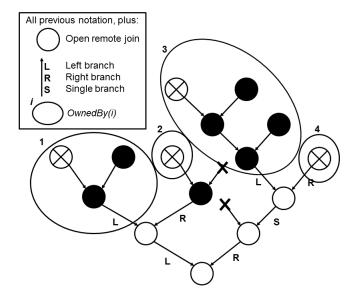

We overcome the second and the third problems by allowing processors to communicate through the join threads. To allow for this, the data structures representing join threads must carry two communication channels for processors running the parent threads. These processors are said to be *watching* this join. A processor may be watching many joins at a time and must periodically check its communication channels for messages. To this end, each processor maintains a *watch list* of joins to be watched. Processors add a join to their watch lists

3

**Figure 1.** An example join resolution.

when a parent thread is stolen and remove it when it is resolved. Adding and removing joins can be done in constant time.

As the example in Figure 1 shows, watch lists must occasionally be transferred between processors when joins are resolved. For example, if the join on thread 5 is resolved such that processor k executes it, i must transfer its watch list to k so that k is aware of its responsibility to watch the join on thread 6. In general, the invariant that we maintain is that the branch of a join is watched by the leftmost processor (in tree order) that works on this branch. Thus, watch list transfers must occur when a left branch is completed and removed from the DAG, changing which processor is leftmost. It is a constant-time operation for a processor to append a transferred watch list to its own. However, since the transfer involves communication between processors, we avoid this operation when possible.

## 3. The Model: Algorithmic X86-TSO

For designing and reasoning about our algorithms, we consider the X86-TSO model [33] for *total-store-order* architectures (e.g., the X86 platform from Intel and AMD) and extend it with a cost model that assigns a cost to each operation. The cost model enables reasoning about termination and efficiency. We refer to this costed model as *algorithmic X86-TSO*, abbreviated as *X86-ATSO*.

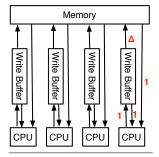

Figure 2 illustrates the abstract X86-TSO machine model [33] for a 4-processor (core/CPU) specimen of the X86 archictecture with total-store order memory system and our cost model. The system consists of a shared memory and one first-in-first-out (FIFO) *store buffer* per processor, each mapping locations to values. When writing a location, the processor simply writes to its store buffer;

**Figure 2.** The X86-TSO model and the costs (in red).

the values stored in the buffer can propagate to memory any time. When reading a location, a processor first consults its store buffer and reads the value written by the most recent store into that location. If the location is not in the store buffer, then the processor accesses the memory.

Many X86 instructions operate locally without requiring synchronization with other processors but some, such as *memory fences* and LOCK'ed instructions, don't. *LOCK'ed* instructions include the atomic XCHG (compare-and-swap) instruction and the atomic versions of the many read-modify-write instruction (ADD, INC, etc) that, when preceded by the LOCK prefix, run atomically. A locked operation starts by taking a global read lock, which prevents all other processors from performing reads, and completes by flushing the store buffer and releasing the lock.

The X86-TSO model does not specify the cost of each operation, nor even termination. For example a memory-fence instruction may not return, or the values written into the store buffers may never propagate to memory. The lack of a cost specification may appear amiss, but it is in fact consistent with hardware because manufacturers do not specify whether the protocols implemented in hardware (e.g., cache coherency) are terminating and how frequently the buffers are flushed.

To design effective algorithms and to prove them correct, terminating, and efficient, a cost model is needed. Such a cost model should at least posit the termination of all operations including memory writes, because otherwise it would not be possible to reason about termination. Therefore, in *algorithmic X86-TSO*, memory reads and writes complete in a single time step, but writes can

take up to an additional finite time,  $\Delta \geq 1$ , to become visible to all processors. Somewhat imprecisely, we illustrate the cost model in Figure 2 by assigning a cost of  $\Delta$  for moving data from the store buffer to memory— $\Delta$  is an upper bound on the time for a write stored in a buffer to make it to memory.

While assuming that each operation takes at most  $\Delta$  steps for some  $\Delta$  may be realistic, we choose not to assume our algorithms are aware of the value of  $\Delta$  for several reasons. First, since  $\Delta$  can vary between different hardware and can be difficult to know, an algorithm designed for a particular  $\Delta$  may not work well in all architectures. Second, the value of  $\Delta$  might be large in the worst case but small in the common case, making an algorithm that uses  $\Delta$  suboptimal. Therefore, our algorithms assume the existence of  $\Delta$  but they don't use it. When reasoning about termination, we assume that some  $\Delta$  exists, without explicitly quantifying it; in other words, we assume that each write eventually makes it to main memory.

## 4. The algorithms

Since we are primarily concerned with the design and the correctness of the algorithm on weak memory models, we present reasonably detailed and precise pseudo-code in C++-like syntax. To remain realistic, we do not assume that we are given a computation DAG to schedule but also construct the DAG dynamically du ring the execution. To express parallelism, we provide one primitive, fork, which can only be called at the end of a parallel thread, specifying the threads to be forked as well as their join. Given a work-stealing framework supporting some basic infrastructural data structures, these algorithms can be employed separately or together to perform load balancing with work stealing and perform join resolution. In fact, our implementation follows closely the pseudo-code and uses these algorithms paired with each other or other algorithms for experimental evaluation. We start by presenting the abstract data types and the data structures for work stealing along with the main scheduling loop and then describe the two algorithms.

#### 4.1 The data structures

4

Several key data structures facilitate our algorithms. One key data structure is a doubly ended queue, a *deque* for short, for storing ready threads. Each processor owns a private deque that can be accessed only by that processor. Each processor operates on the deque following the work-stealing paradigm, by pushing new parallel threads at the bottom of the deque, and popping threads from the bottom when it completes the execution of a thread (with push\_bottom, pop\_bottom operations). Since deques are not concurrent, there is no need for memory fences, which would otherwise be needed at every pop\_bottom operation.

Figure 3 specifies the other data types and structures used in our algorithm. The type query is used by the load-balancing algorithm for packing an identifier and a round number into a single machine word. A *query* consists of the identity of a processor and of a round number. For correctness, it is critical for processors to be able to make queries atomically. We therefore represent a query as a single 64-bit machine word (type query), using 24 bits for the identifier and 40 bits for the round number (which makes it possible to support computations up to  $2^{40}$  rounds with up to  $2^{24}$  processors). The function q\_make constructs a query, and the functions q\_id and q\_rnd project out the ID and the round numbers of the offer, respectively.

The enumeration types stat and side are used by the joinresolution algorithm. The record thread, used to represent a thread, has three fields: the status field is an array of size two used by the join algorithm to keep track of the completion of the dependencies (if any) of this thread. These could be ACK indicating that the branch will complete last, READY indicating that the branch

```

1 // Query type with 40-bit round numbers.

// Representation of threads

type thread = {

2

type query = unsigned_int_64

20

stat status[2]; // state of dependencies

3

query q_make(int i, int r)

21

return r + (i << 40)

22

void run();

// body of the thread

int q_id(query q)

23

cont conti; }

// continuation

5

6

return (q >> 40)

24

25

// Representation of continuations

7

int q_rnd(query q)

return (q & ((1 << 40)-1))

type cont = {

8

26

9

27

thread* join;

// end-point of the edge

side branch; }

// position of the edge

10

// Constants for representation of threads.

28

11

type stat = | WORK

29

30

I ACK

// Global variables.

12

deque < thread *> deque [P] = {DEQUE_EMPTY, ..}

13

I READY

31

| TRANSFER { set < cont > * }

cont cur_cont[id]

14

set < cont > watching[P] = {SET_EMPTY, ..}

33

15

type side = int

int round[P] = {1, ...}

query in_query[P] = {q_make(0,0), ...}

16

const side LEFT = 0

34

const side RIGHT = 1

35

17

thread* received[P] = {NULL, ...}

const side SINGLE = 2

36

```

Figure 3. Data types and global state.

5

has finished earlier than or concurrently with the other branch, WORK indicating that the branch has not been yet completed, and TRANSFER indicating the transfer of a watch list. These values, along with a pointer to the watch lists in the case of TRANSFER, can be packed into a single word and thus can be written atomically. The run method corresponds to the body of the thread, and the conti field describes the *continuation* of the thread. The continuation (type cont) consists of a pointer on a join thread, which has the current thread as a dependency, and a branch value, which indicates whether the current thread is the left, the right, or the single dependency of the join thread.

The shared state (global variables) include deques (called deque in the pseudo-code), current continuations (cur\_cont), the watch lists (watching) defined as a set of items describing continuations that this processor must check for messages regarding join resolution. The other global variables (round, in\_query and received) are used for work stealing. All these variables are processor-indexed arrays.

## 4.2 The main scheduling loop

Figure 4 shows the pseudo-code of the main scheduling loop, function main. Like all other functions of the algorithm, this function takes as first argument the ID of the processor calling it. If a processor finds its deque empty, then it calls acquire to obtain a thread. Otherwise, it pops the thread at the bottom of its deque and executes it, after remembering the continuation of this thread. After the thread completes, the processor handles the continuation using the function handle\_cont, described below.

The fork function (Figure 4) takes as arguments the ID of the caller, the left branch thread, the right branch thread, and the join thread. When the currently-running thread calls fork, the current continuation is captured and used as a continuation of the join thread, while the current continuation is set to point to a NULL pointer. We set the status fields of the join thread to WORK in order to indicate that neither branch has completed execution. The left and right threads are then pushed onto the deque, after their continuation is set as the join thread and marked with the corresponding branch (LEFT or RIGHT). Note that the content of the status field of the branch threads is irrelevant because the threads are ready when created.

Figure 5 contains the code of the function handle\_cont for handling continuations. If the continuation describes the end of the entire computation (END), the program exits. If the continuation carries a null pointer, indicating that the thread that has just run has forked, there is nothing to do. Otherwise, the continuation carries a valid thread pointer c.join and a branch value, which is one of

SINGLE, LEFT or RIGHT. The value SINGLE captures the fact that the thread that has just run was the unique dependency on the join thread, so the join thread can be scheduled immediately. Otherwise, in the particular case where the thread that has just finished is a left branch and the corresponding right branch is still in the deque (it was not sent away), the remaining right branch can be safely converted into a single branch. In other cases, it must be that the left branch and the right branch are running on different processors, and therefore the join resolution algorithm needs to be invoked.

#### 4.3 Our Work-Stealing Algorithm

To perform load balancing via steals without memory fences and atomic read-modify-write operations operations, our algorithm relies on explicit communication between processors and local operations on deques. To communicate, each processor periodically calls the function communicate. (Such periodic calls can be implemented using several known techniques (e.g., [1] and references thereof.) Since when exactly communication takes place does not affect correctness as long as it takes place within the main body of the scheduler (or by trapping into the scheduler from the user code), we do not discuss this any further.

For load balancing, each processor maintains a *round* number to differentiate between its own *phases*: starting from zero, the round number gets incremented every time the processor serves or declines a (steal) query. Each processor also uses two shared memory cells: an *in-query* cell (in\_query) for receiving queries from idle processors, and a *reception* cell (received) for receiving thread pointers from busy processors.

The load-balancing algorithm (Figure 6) consists of two functions, called acquire and communicate. A processor calls acquire when its deque is empty. It starts by writing a null pointer in its reception cell, and then repeatedly attempts to acquire work from another randomly picked victim processor. To acquire work, it first checks that the victim admits queries by checking that the round number of the last query targeting the victim is less than victim's current round number. If so, then the processor writes a query containing its own identifier and the victim's round number into the victim's in-query field. The victim serves the query when it calls communicate. If a thread is delivered, the processor receives the thread, and updates its watch list to coordinate the resolution of the join with the victim. Otherwise the processor tries to steal again.

When a busy processor calls communicate (which it does periodically), it first reads its in\_query field. If it finds a query whose round number matches its round number, then it means that (at least) one idle processor is waiting for an answer to its query. To serve the query, the processor checks if it has a thread that it can

```

void main(int i)

void fork(int i, thread* t1, thread* t2, thread* tj)

38

while true do

46

tj.conti = cur_cont[i]

cur_cont[i].join = NULL

39

if deque[i].is_empty()

47

40

acquire()

tj.status[LEFT] = WORK

thread* t = deque[i].pop_bottom()

tj.status[RIGHT] = WORK

41

49

42

cur_cont[i] = t.conti

50

t1.conti = cont { tj, LEFT }

t2.conti = cont { tj, RIGHT }

51

43

t. run ()

44

handle_cont(i, cur_cont[i])

52

deque[i].push_bottom(t2)

53

deque[i].push_bottom(t1)

Figure 4. Main loop and fork function.

```

```

54 // Called after completion of a thread

61

else if (c.branch == LEFT

void handle_cont(int i, cont c)

62

&& not deque[i].empty())

if c.join == END then exit(0)

// Optimize the local right branch

63

if c.join == NULL then return

thread* t = deque[i].peek_bottom()

57

64

if c.branch == SINGLE

65

t.conti.branch = SINGLE

58

59

deque[i].push_bottom(c.join)

66

else

60

67

resolve_join(i, c)

```

**Figure 5.** Handling of continuations.

```

91 // Called periodically by a busy processor

// Called when a worker runs out of work

void acquire(int i) // i = ID of caller

void communicate(int i) // i = ID of caller

// Check for incoming queries

received[i] = NULL

93

while true

94

query q = in_query[i]

int j = random \in \{0, ..., P-1\}\setminus\{i\}

95

if q_rnd(q) != round[i]

int r = round[j]

96

return

// Test whether target accepts queries

97

// Process the incoming query

98

if q_rnd(in_query[j]) < r</pre>

if size(deque[i]) > 0

// Send a query

99

&& peek_top(deque[i]).conti.branch == RIGHT

in_query[j] = q_make(i, r)

100

thread* t = pop_top(deque[i])

cont conti = {t.conti.join, LEFT}

while round[j] == r

101

// Resend same query if needed

102

watching[i].push(conti)

if q_rnd(in_query[j]) < r</pre>

103

received[q_id(q)] = t

in_query[j] = q_make(i, r)

104

round[i]++ // Starts a new query phase

105

block(i)

// Receive the thread, if any

106

// Auxiliary function for blocking queries

thread* t = received[i]

107

void block(int i) // i = ID of caller

if t != NULL

108

int r = round[i]

watching[i].push(t.conti)

109

if in_query[i] != q_make(i,r)

in_query[i] = q_make(i, r+1)

push_bottom(deque[i], t)

110

round[i] = r+1

round[i]++ // Accept queries

111

return

```

Figure 6. Load-balancing algorithm.

6

send. If so, it pops the thread from its deque, writes the corresponding thread pointer into the reception cell of the querying processor, and updates its watch list to coordinate with the thief. If not, the query cannot be served. In both cases, the processor increments its round number to implicitly notify all processors that made queries at the current round. A querying processor is thus able to detect whether its query was served or declined by testing whether its reception cell contains a non-null value.

The implementation of the function acquire involves two small complications. First, for efficiency, an idle processor should discourage other idle processors from making queries to it. To that end, an idle processor uses the auxiliary function block for making a query to itself (leaving it unanswered), thereby preventing other processors from making a query. Second, when an idle processor makes a query to a busy processor, it needs to ensure that, if its query gets overwritten by another query tagged with an out-of-date round number, then it resends its query. Without such a resend operation, the busy processor targeted would simply ignore the out-of-date query and never increment its round number.

## 4.4 Our Join-Resolution Algorithm

68

69

70

71

72 73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

block(i)

Figure 7 illustrates the pseudo-code for the join resolution algorithm. When a processor i completes executing a parent of a join thread, it calls the function resolve\_join with the continuation

for that join thread. The continuation consists of the join thread and an identification of the parent; side = LEFT = 0 means the left parent and side = RIGHT = 1 means the right parent. We start by checking the status field of the join for the parent that has just been completed. If the status field is ACK, then the other parent has completed and the join thread is ready for execution. We therefore push the thread into the bottom of the processor i's deque. If the status field is not ACK, then the parent has finished first or concurrently with the other parent. In this case, we set the status field of the join for this parent to READY and remove this continuation from the watch list of the processor. We then wait until we receive an ACK from the other processor watching the join or see that it is READY. If we receive an ACK, then this parent has finished first and thus the join has to wait for the other parent to complete. If this is the left branch, however, we first transfer the watch list of processor i to the other processor by making it available as part of the status field. If we receive a READY, then both parents completed at the same time and the processor that executed the left branch pushes the join thread into its deque (breaking the tie in this way avoids transfering the watch list.)

The function watch, which is periodically called by each processor, acknowledges the receipt of READY messages from other parents of the join that the processor i is watching, and transfers

```

112 // Called to resolve a non-local join

// Called periodically by a busy processor

void watch(int i)

void resolve_join(int i, cont c)

134

113

foreach (cont c) in watching[i]

114

int b1 = c.branch

135

115

int b2 = 1 - b1

136

int b1 = c.branch

int b2 = 1 - b1

int* status = c.join.status

137

116

117

if status[b1] == ACK // Finish second.

138

int* status = c.join.status

deque[i].push_bottom(c.a.join)

if status[b2] == READY

139

118

// Other branch done

119

else // May have finished first

140

120

status[b1] = READY

141

status[b1] = ACK

watching[i].remove(c)

121

watching[i].remove(c)

142

122

while status[b2] == WORK

143

if b1 == LEFT

noop // May call watch here

123

144

continue

124

match status[b2] with

145

// Reception of the watch list

125

ACK:

146

while status[b2] == READY

if b1 == LEFT // Transfer watch list

126

147

{\tt noop} // May call watch

127

set < cont > * s = watching[i].copy()

148

match status[b2] with

status[b1] = TRANSFER{s}

| TRANSFER(s):

128

149

watching[i].remove_all()

watching[i].add_multiple(s)

129

150

130

| READY:

if b1 == LEFT // Resolve race to left

131

132

deque[i].push_bottom(c.join)

```

Figure 7. Join resolution algorithm.

7

watch lists when necessary. To this end, it checks, for each join, whether the other parent is READY. If so, it acknowledges by writing ACK to the status field of the join, indicating that this parent will be responsible for the join and stops watching the join. If this parent in the right branch, it transfers the watch list from the left parent.

#### 5. Correctness

To prove the correctness of our algorithms, we must first define what correctness means. We do this by building a formal, dynamic notion of a valid scheduler and then proving a correspondence between this formal notion and our concrete algorithm. Full details of the (12-page) proof appear in the appendix.

**Assumptions.** For the proof, we assume the X86-ATSO model described in Section 3. In particular, we assume that there exists a fixed (but unknown) upper bound  $\Delta$  on the time in which writes are flushed to memory. We also make a (relatively weak) fairness assumption concerning the scheduling of our threads by the operating system: if a concrete execution does not terminate, then every processor takes infinitely many steps.

**Proof Outline.** We formalize a valid scheduler as an *abstract semantics*. The abstract semantics that we consider is presented as a reduction relation on the *abstract state*, which is an idealized view of the parallel computation to be performed. More precisely, the abstract state consists of a quadruple of the form (N, E, X, M). The pair (N, E) corresponds to the *computation DAG*, in which threads are represented as nodes and dependencies between threads are represented as edges. The map X maps each processor to the thread that it runs, if any. (Technically, X also includes the not-yet-run code of the running threads.) The variable M describes the *application state*. M is a concrete representation of memory that follows the X86-ATSO model, but contains only the application memory and not the data structures used by our scheduler.

The abstract semantics consists of transitions between abstract states, written  $A \longrightarrow A'$ . There are four possible transitions from a state (N, E, X, M). First, an idle processor (i.e. a processor bound by X to no thread) may be associated a ready thread (i.e., a node from N that has no incoming edge according to E). Second, a processor may execute one atomic instruction from its assigned thread; as a result, the application state M may be updated. The remaining two transitions describe the case of a processor that completes a thread and then becomes idle, after removing from N the corresponding node and removing from E all associated

edges. Which of the two rules applies depends on whether the last operation performed by the thread is a fork operation. Formal rules for these transitions are given in the appendix.

The initial abstract state, called  $A_0$ , is defined as  $(\{n_0\}, \emptyset, \emptyset, \emptyset)$ , where  $n_0$  is the initial thread. This thread describes the entire parallel computation in the sense that it will fork other threads, which themselves fork other threads which eventually build the entire computation DAG. When it terminates, an abstract execution reaches a state of the form  $(\emptyset, \emptyset, \emptyset, M)$ , where M, the final application state, typically contains the final result of the computation. We use the abstract semantics as a model for all valid schedulers.

The concrete state corresponds to the state of our program code (including scheduling code) at a given point in time. A concrete state C includes the code pointer of each of the processors and the content of all the shared memory. C includes the application memory, which is identical to the M component of the abstract state, as well as the data structures used by the scheduler such as the set of allocated thread objects, the state of the deques, etc. We project out the application memory component of C by writing  $\operatorname{Mem}(C)$ . The initial concrete state, written  $C_0(n_0)$ , describes a state where all deques are empty, except that of one processor, which holds the initial thread corresponding to the initial node  $n_0$ . Transitions on the concrete state, written  $C \Longrightarrow C'$ , correspond to execution of one atomic instruction by one of the processor or one flush from a write buffer into shared memory.

Our theorem, stated below, has two parts. The first half (correctness) asserts that if there is a reduction sequence for the concrete execution that terminates on a memory state C, then there exists a reduction sequence for the abstract state that reaches a state with application memory  $\mathrm{Mem}(C)$ . The second part (liveness) asserts that if the concrete execution may diverge, there there exists a reduction sequence for the abstract state that diverges as well.

**Theorem 5.1** (Correctness and liveness). For any initial thread node  $n_0$ , and for any concrete state C in which all processors have run out of threads and are running acquire,

$$C_0(n_0) \Longrightarrow^* C$$

implies  $(\{n_0\}, \emptyset, \emptyset, \emptyset) \longrightarrow^* (\emptyset, \emptyset, \emptyset, \operatorname{Mem}(C))$

$C_0(n_0) \Longrightarrow^{\infty}$  implies  $(\{n_0\}, \emptyset, \emptyset, \emptyset) \longrightarrow^{\infty}$

Note that, in the particular case of a *deterministic* terminating parallel program, our theorem implies that if the program reaches some application state in the abstract semantics, then it also reaches this application state in the concrete semantics.

The proof of the correctness result is based on a simulation lemma. This lemma shows that we are able to exhibit a relation R between abstract and concrete states, such that any action taken by the algorithm corresponds (in a way defined by the relation R) to an abstract transition, that is, to an allowed action of a scheduler.

**Lemma 5.2** (One-step simulation). There exists a relation R for which the following implication holds: if  $C \Longrightarrow C'$  and RCA, then there exists A' such that  $A \longrightarrow^* A'$  and RC'A'.

The definition of R includes relations between the data structures of the algorithm code and the components of the abstract state, as well as all the invariants of the concrete state that are required to show that our algorithms are correct. These invariants are stated in terms of the main memory and the state of the write buffers associated with the processors.

To make this proof tractable and more modular, we separate the write buffers into one buffer per core and per memory location. Since there are situations where the order between the writes is crucial, we associate with each write a (logical) time-stamp. These time-stamps, local to each processor, allow us to express in our invariants comparisons between the times of writes by the same processor to two different locations. In addition to Lemma 5.2, we show that the flush of any write from a buffer to main memory preserves all the invariants.

## 6. Efficiency

At a high level, the behavior of our load balancing algorithm is very close to the compare-and-swap-based, receiver-initiated work stealing algorithm with private deques [1], which has been proved efficient. We believe that, under the assumption that the time taken by write operations to reach the main memory (the time bounded by  $\Delta$ ) follows a Poisson distribution, it would be possible to extend that proof to prove a similar result for our work-stealing algorithm. We find this assumption rather unrealistic, however. Without the assumption, it seems that a different proof technique might be needed. Setting up such proof is beyond the scope of this paper.

In this section, we discuss rather informally (mostly without proof) the key aspects regarding the efficiency of our algorithms. Following the presentation of the proof of the CAS-based algorithm [1], we let  $\tau$  denote the average delay between calls to the functions communicate and watch. As established by the proof, for parallel computations exhibiting a reasonable amount of parallelism,  $\tau$  can be set to a large value without adversely affecting performance. In particular, for most practical purposes, we can assume  $\tau$  to be at least an order of magnitude greater than  $\Delta$ , which is a rather small value.

Efficiency of the work stealing algorithm. A successful steal operation involves sending a query, which takes no more than  $\Delta$ , waiting for the targeted processor to call communicate, which takes  $\tau$  on average, and receiving the answer, which takes no more than  $\Delta$ . Overall, instead of the  $\tau$  bound on the successful steal operations in the CAS-based algorithm [1], we now have a bound of  $\tau+2\Delta$ . This overhead, charged to the steals, is relatively small. Successful steals always steal the top task in the target's deque and the stolen task starts executing immediately afterwards.

Unsuccessful steals are slightly more delicate to analyze, because of the stale queries, which may appear to slow down the load balancing process. We argue that stale queries in fact do not harm performance. When a processor increments its round number, this number is seen by all other processors after a delay of  $\Delta$ . Therefore, after a  $2\Delta$  delay, a processor cannot receive stale queries, unless it has incremented its round number in the meantime. In other words, unless the processor goes idle or serves a valid query, after a period of  $2\Delta$ , we know that this processor can only receive valid queries. Stale queries therefore can cause a small delay to successful steals.

When  $\tau \gg \Delta$ , stale queries are even less likely. (Indeed, in our experiments, we rarely observed stale queries; the few that were observed could be due to swapping of workers by the operating system.)

Efficiency of the join-resolution algorithm. Our join resolution algorithm operates on watch lists in constant time, except for the watchlist traversal operation. We therefore show that items contained in all watchlists, summed over all P processors, does not exceed P-1. This result suffices to show that the relative, amortized overhead associated with periodic checking of watchlists does not exceed  $O(1/\tau)$  per processor. The proof of this result, detailed in Appendix C, relies on the intuition that the number of open interprocessor joins does not exceed P-1. Intuitively, since the processors are always working on disjoint sub-DAGs of the computation DAG, the paths in the DAG from these sub-DAGs down to the final join form a reverse tree structure. This tree has P leaves (the sub-DAGs), so it cannot have more than P-1 nodes of arity 2 (the open join nodes).

## 7. Experiments

Because atomic read-modify-write operations are quite efficient on current multicore computers, especially when they are rare as in the state-of-the art implementations of work stealing, we do not expect our algorithms to outperform state-of-the-art implementations on today's multicore computers. Our work is primarily motivated by the theoretical question of whether atomic read-modify-write operations may be eliminated completely and with the possibility that such operations may be absent from future hardware or may not be efficient. Nevertheless, we feel that an experimental evaluation on current hardware would be valuable to assess the implementabality and practicality of the algorithms. We report some of our findings here; the reader can find more details in the submitted appendix.

Implementation and experimental setup. We implemented our algorithms in the context of a C++ library for multithreading and evaluated them with a relatively broad range of benchmarks. Our implementation creates one POSIX thread (i.e., pthread) for each core available, and allows for dynamically selecting a scheduler of our choice, leaving the rest of the code the same. As basis for comparison, we used two other schedulers: first, a publicly available implementation of the CAS-based private-deques algorithm [1] and, second, our own implementation of the Chase-Lev [9] algorithm. In addition, we compare our work to Cilk Plus, which is an extension of GCC that implements an algorithm that is similar to Chase-Lev. Cilk Plus benefits from many years of careful engineering and sets a high standard for the performance of our algorithm. The privatedeques algorithm, on which our algorithm is based, helps us isolate the cost of our steal protocol and compare it to the cost of performing steals with CAS instructions. Our own implementation of the Chase-Lev algorithm, even though it is not as optimized as Cilk Plus's implementation, helps us isolate the effect of the difference between our benchmarks and Cilk bencmarks, when needed.

For the parallel executions, all schedulers produce exactly the same computation DAG for all benchmarks, with the exception of the *sort* benchmark, for which Cilk Plus is using a different granularity control technique for the parallel loops (creating 8P subtasks). For our measurements, we used a 32-core, 2.0GHz Intel machine with 1Tb of RAM (our benchmarks use a fraction of the available memory). We consider just 30 out of the 32 total cores in order to reduce interference with the operating system. The baseline performance is, for each benchmark, from the single-core run time of the purely-sequential version of the code. To tame the variance observed in the measures when running with 30 cores (usually 5% to 10% noise), we averaged the measures over 20 runs.

2013/11/27

|                       | PD/CAS    | PD/CAS | Our   | Our   |                       | Cilk      | Cilk  | Chase | Our   | Our   |

|-----------------------|-----------|--------|-------|-------|-----------------------|-----------|-------|-------|-------|-------|

|                       |           |        | WS    | WS+JR |                       | Plus      | Plus  | Lev   | WS    | WS+JR |

|                       | (speedup) | (sec)  | (%)   | (%)   |                       | (speedup) | (sec) | (%)   | (%)   | (%)   |

| matmul                | 26.1      | 2.1    | -0.0  | +2.2  | matmul                | 23.3      | 2.4   | +7.0  | -10.8 | -8.8  |

| cilksort (exptintseq) | 19.1      | 1.3    | -0.1  | +14.3 | cilksort (exptintseq) | 20.1      | 1.2   | +7.1  | +5.4  | +20.5 |

| cilksort (randintseq) | 22.2      | 1.5    | -0.2  | +8.1  | cilksort (randintseq) | 23.0      | 1.4   | +4.6  | +3.5  | +12.1 |

| fib                   | 27.5      | 3.7    | -1.9  | +0.9  | fib                   | 25.7      | 4.0   | -5.6  | -8.6  | -5.9  |

| matching (eggrid2d)   | 19.4      | 1.6    | +5.4  | +13.6 | matching (eggrid2d)   | 17.6      | 1.7   | +7.2  | -4.1  | +3.4  |

| matching (egrlg)      | 19.4      | 4.1    | +0.7  | +7.7  | matching (egrlg)      | 19.7      | 4.0   | +9.5  | +2.4  | +9.4  |

| matching (egrmat)     | 18.9      | 3.6    | -0.7  | +7.2  | matching (egrmat)     | 18.5      | 3.6   | -1.8  | -2.8  | +5.0  |

| MIS (grid2d)          | 15.7      | 0.8    | -11.2 | +9.8  | MIS (grid2d)          | 16.8      | 0.7   | +13.2 | -5.2  | +17.3 |

| MIS (rlg)             | 18.8      | 1.9    | -0.9  | +13.4 | MIS (rlg)             | 18.2      | 2.0   | +3.0  | -3.9  | +9.9  |

| MIS (rmat)            | 19.0      | 2.1    | -1.6  | +12.6 | MIS (rmat)            | 17.3      | 2.3   | +6.1  | -10.4 | +2.4  |

| hull (plummer2d)      | 17.3      | 2.3    | -3.5  | -2.4  | hull (plummer2d)      | 19.8      | 2.0   | +8.0  | +10.6 | +11.8 |

| hull (uniform2d)      | 18.3      | 4.4    | -0.4  | +1.5  | hull (uniform2d)      | 18.9      | 4.2   | +3.6  | +2.8  | +4.8  |

| sort (exptseq)        | 23.3      | 1.6    | -0.9  | +0.7  | sort (exptseq)        | 15.0      | 2.5   | -38.5 | -36.0 | -35.0 |

| sort (randdblseq)     | 24.4      | 2.2    | -1.3  | +1.3  | sort (randdblseq)     | 15.0      | 3.5   | -40.1 | -39.2 | -37.7 |

**Table 1.** Comparison with private-deques algorithm with CAS's and fetch-and-add (smaller % is better).

Table 2. Comparison with Cilk Plus and Chase Lev (smaller % is better).

**Benchmarks.** As benchmark, we consider three classic programs ported from Cilk and a number of programs from Blelloch et al.'s recent problem-based benchmark suite (PBBS) [3]. Cilk benchmarks include cilksort, which is based on a parallel version of merge-sort; matmul, which multiplies two dense matrices in place using a cache-efficient, divide-and-conquer algorithm [16]; and fibonacci, which computes Fibonacci number using the exponential algorithm. (This last benchmark is useful to perform analyses without observing interference from the memory.) PBBS benchmarks include internally-deterministic parallel programs targeting Cilk: matching, which computes the maximal matching of an undirected graph; MIS, which computes the maximal independent set of an undirected graph; hull, which computes a 2-dimensional convex hull; and sample-sort, which is a low-depth, cache-efficient version of the classic sample sort algorithm. Note that two of the benchmark programs, namely matching and MIS, make use of atomic CAS instructions [3], but the others do not.

Terminology. We use the following terminology: "Our WS" refers to our work-stealing algorithm that uses no atomic readmodify-write instructions for stealing work but uses fetch-and-add operations for join resolution; "Our JR" refers to our join-resolution algorithm with no atomic read-modify-write operations. We use our join-resolution algorithm only with our work-stealing algorithm. "Our WS+JR" refers to this algorithm. "PD/CAS" refers to the private-deques algorithm with CAS-based steals. "Chase Lev" refers to our implementation of the Chase-Lev algorithm. "Cilk Plus" refers to Cilk Plus. All these approaches ("PD/CAS", "Chase Lev", and "Cilk Plus" use the optimized fetch-and-add based join resolution (Section 2).

Work Stealing. To understand the overheads of our work-stealing algorithm (described in Section 4.3), we can compare its performance to the private-deques algorithm with CAS's, which differs from our algorithm only in how the steals are performed. Table 1 reports on the absolute speedups of these algorithms and on the the relative differences between the three. Our algorithm is consistently the same or slightly faster, except for one case where it is 5% slower. Our algorithm is on average 1.2% faster. These measurements show that even on current architectures, where CAS operations are cheap, there is no measurable overhead to eliminating them from work stealing.

Table 2 gives the speedup and absolute run time of Cilk Plus and gives the relative value of the run time of the other algorithms: the Chase-Lev algorithm, our work-stealing algorithm, and our work-

stealing algorithm with our join-resolution algorithm. Compared with Cilk Plus, our work-stealing algorithm (the second column from the last) is in some case faster and in some cases slower, but never more than 10% slower. Compared to Chase Lev, our algorithm is almost always faster—on average, 6.9% and 5.6% faster compared to Cilk and Chase Lev respectively. For sorting benchmarks *sort*, the run time of Cilk Plus is quite poor. As measurements with Chase-Lev confirms, this is due to the different treatment in Cilk Plus of the granularity in parallel loops. These measurements indicate that our work-stealing algorithm is competitive with the state of the art CAS-based work-stealing algorithms.

Our join-resolution algorithm. As can be seen in Tables 1 and 2, by comparing the last two columns, our atomic-read-modify-write-free join resolution algorithm is slower, by at most 15% but usually less than 5%, than the optimized fetch-and-add algorithm for join resolution employed by the other schedulers. To understand why it is slower, we examined in more detail the statistics of the worst case, namely cilksort(exptintseq). From the statistics, we were able to rule out factors such as higher latency or larger total-parallel-work. Few potential factors remain. One is the overhead of maintaining watch lists. These findings suggest that 1) join resolution with atomic read-modify-write operations performs well on current architectures, and 2) that join resolution without atomic read-modify-write instructions can be noticeably slower, which might become an important issue in future, larger-scale architectures.

#### 8. Related work

While there is a lot of work on scheduling for parallel computations on hardware shared memory machines, all of the previous work relies on synchronization operations such as locks, memory fences, and atomic read-modify-write operations [2, 5, 9, 16, 31]. Some research has looked into eliminating memory fences, sometimes by weakening the correctness guarantees of work stealing [29], some in the general case [14, 15, 18, 20, 32, 34]. Recent work shows that memory fences can be eliminated from work stealing without detrimentally effecting efficiency [1].

The cost of synchronization in concurrent algorithms has been an important subject of study. Non-blocking algorithms and data structures [19] disallow the use of locks but rely instead on atomic read-modify-write operations such as compare-and-swap. The algorithms that we propose appear to be non-blocking due to the absence of any locks and other synchronization operations but they are not wait-free because an idle worker can wait for another busy

worker indefinitely if that worker is suspended by the operating system. This problem, however, appears not too difficult to remedy.

To eliminate memory fences and atomic read-modify-write operations, our algorithms use explicit communication between processors. Our algorithms therefore have some similarities to distributed algorithms, which communicate by message passing. There has been much work on distributed scheduling algorithms considering both the receiver- and sender-initiated approaches [1, 10, 11, 13, 30]. In the sender-initiated approach, busy processors periodically share work with other idle (low-load) processors; in the receiver-initiated approach idle (low-load) processors demand work from busy (high-load) processors. Both approaches perform quite well though certain specifics regarding delays and system load can make one preferable over the other. Our algorithms differ from distributed algorithms because they use shared memory for storing the shared state (e.g., threads) between processors. In addition, for efficient steals, our work-stealing algorithm allows certain data races; for efficient join resolutions, it carefully creates and manages message channels.

#### 9. Conclusion

This paper shows that it is possible to perform work-stealing and join-resolution without atomic read-modify-write operations and memory fences. In our algorithms, as in distributed algorithms, processors communicate explicitly. Unlike in distributed algorithms, our algorithms take advantage of shared memory by, for example, sharing state and permitting and taking advantage of data races. Our algorithms seem practically efficient, and we informally reason, but do not prove, that they are efficient in theory. Such proofs, left to future work, seem non-trivial especially because of the partial-synchrony-like assumptions required to account for the effects of the weak memory model.

#### References

- Umut A. Acar, Arthur Charguéraud, and Mike Rainey. Scheduling parallel programs by work stealing with private deques. In ACM SIG-PLAN Symposium on Principles and Practice of Parallel Programming (PPOPP), 2013.

- [2] Nimar S. Arora, Robert D. Blumofe, and C. Greg Plaxton. Thread scheduling for multiprogrammed multiprocessors. In *Proceedings of* the tenth annual ACM symposium on Parallel algorithms and architectures, SPAA '98, pages 119–129. ACM Press, 1998.

- [3] Guy E. Blelloch, Jeremy T. Fineman, Phillip B. Gibbons, and Julian Shun. Internally deterministic parallel algorithms can be fast. In Proceedings of the 17th ACM SIGPLAN symposium on Principles and Practice of Parallel Programming, PPoPP '12, pages 181–192, New York, NY, USA, 2012. ACM.

- [4] Guy E. Blelloch and John Greiner. A provable time and space efficient implementation of NESL. In *Proceedings of the 1st ACM SIGPLAN International Conference on Functional Programming*, pages 213–225. ACM, 1996.

- [5] Robert D. Blumofe, Christopher F. Joerg, Bradley C. Kuszmaul, Charles E. Leiserson, Keith H. Randall, and Yuli Zhou. Cilk: an efficient multithreaded runtime system. In ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming (PPOPP), pages 207–216, 1995.

- [6] Robert D. Blumofe and Charles E. Leiserson. Scheduling multithreaded computations by work stealing. J. ACM, 46:720–748, September 1999.

- [7] F. Warren Burton and M. Ronan Sleep. Executing functional programs on a virtual tree of processors. In *Functional Programming Languages* and Computer Architecture (FPCA '81), pages 187–194. ACM Press, October 1981.

- [8] Philippe Charles, Christian Grothoff, Vijay Saraswat, Christopher Donawa, Allan Kielstra, Kemal Ebcioglu, Christoph von Praun, and Vivek Sarkar. X10: an object-oriented approach to non-uniform cluster computing. In *Proceedings of the 20th annual ACM SIGPLAN*

- conference on Object-oriented programming, systems, languages, and applications, OOPSLA '05, pages 519–538. ACM, 2005.

- [9] David Chase and Yossi Lev. Dynamic circular work-stealing deque. In ACM Symposium on Parallelism in Algorithms and Architectures, SPAA '05, pages 21–28, 2005.

- [10] Sivarama P. Dandamudi. The effect of scheduling discipline on dynamic load sharing in heterogeneous distributed systems. *Modeling, Analysis, and Simulation of Computer Systems, International Sympo*sium on, 0:17, 1997.

- [11] J. Dinan, S. Olivier, G. Sabin, J. Prins, P. Sadayappan, and C.-W. Tseng. Dynamic load balancing of unbalanced computations using message passing. In *Parallel and Distributed Processing Symposium*, 2007. IPDPS 2007. IEEE International, pages 1 –8, march 2007.

- [12] Cynthia Dwork, Nancy Lynch, and Larry Stockmeyer. Consensus in the presence of partial synchrony. *Journal of the ACM*, 35:288–323, April 1988.

- [13] Derek L. Eager, Edward D. Lazowska, and John Zahorjan. A comparison of receiver-initiated and sender-initiated adaptive load sharing. *Perform. Eval.*, 6(1):53–68, 1986.

- [14] Marc Feeley. A message passing implementation of lazy task creation. In *Parallel Symbolic Computing*, pages 94–107, 1992.

- [15] Matthew Fluet, Mike Rainey, John Reppy, and Adam Shaw. Implicitly threaded parallelism in Manticore. *Journal of Functional Program*ming, 20(5-6):1–40, 2011.

- [16] Matteo Frigo, Charles E. Leiserson, and Keith H. Randall. The implementation of the Cilk-5 multithreaded language. In *PLDI*, pages 212–223, 1998.

- [17] Robert H. Halstead, Jr. Implementation of multilisp: Lisp on a multiprocessor. In *Proceedings of the 1984 ACM Symposium on LISP and functional programming*, LFP '84, pages 9–17. ACM, 1984.

- [18] Danny Hendler and Nir Shavit. Work dealing. In Proceedings of the fourteenth annual ACM symposium on Parallel algorithms and architectures, SPAA '02, pages 164–172. ACM, 2002.

- [19] Maurice Herlihy. A methodology for implementing highly concurrent data objects. ACM Trans. Program. Lang. Syst., 15(5):745–770, November 1993.

- [20] Tasuku Hiraishi, Masahiro Yasugi, Seiji Umatani, and Taiichi Yuasa. Backtracking-based load balancing. In ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming, pages 55–64. ACM, 2000

- [21] Jason Howard, Saurabh Dighe, Sriram R. Vangal, Gregory Ruhl, Nitin Borkar, Shailendra Jain, Vasantha Erraguntla, Michael Konow, Michael Riepen, Matthias Gries, Guido Droege, Tor Lund-Larsen, Sebastian Steibl, Shekhar Borkar, Vivek K. De, and Rob F. Van der Wijngaart. A 48-core ia-32 message-passing processor with dvfs in 45nm cmos. J. Solid-State Circuits, (1):173–183.

- [22] Intel. Cilk Plus. http://software.intel.com/en-us/ articles/intel-cilk-plus/.

- [23] Intel. Intel Xeon Processor X7550. Specifications at http://ark.intel.com/products/46498/ Intel-Xeon-Processor-X7550-(18M-Cache-2\_00-GHz-6\_ 40-GTs-Intel-QPI).

- [24] Gabriele Keller, Manuel M.T. Chakravarty, Roman Leshchinskiy, Simon Peyton Jones, and Ben Lippmeier. Regular, shape-polymorphic, parallel arrays in haskell. In *Proceedings of the 15th ACM SIG-PLAN international conference on Functional programming*, ICFP '10, pages 261–272, 2010.

- [25] Sanjeev Kumar, Christopher J. Hughes, and Anthony Nguyen. Carbon: architectural support for fine-grained parallelism on chip multiprocessors. SIGARCH Computer Architecture News, 35:162–173, June 2007.

- [26] Leslie Lamport. Specifying concurrent program modules. ACM Trans. Program. Lang. Syst., 5(2):190–222, April 1983.

- [27] Doug Lea. A java fork/join framework. In Proceedings of the ACM 2000 conference on Java Grande, JAVA '00, pages 36–43, 2000.

- [28] Daan Leijen, Wolfram Schulte, and Sebastian Burckhardt. The design of a task parallel library. In Proceedings of the 24th ACM SIGPLAN conference on Object oriented programming systems languages and applications, OOPSLA '09, pages 227–242, 2009.

- [29] Maged M. Michael, Martin T. Vechev, and Vijay A. Saraswat. Idempotent work stealing. In *Proceedings of the 14th ACM SIGPLAN Sym*posium on *Principles and Practice of Parallel Programming (PPoPP)*, pages 45–54, 2009.

- [30] R. Mirchandaney, D. Towsley, and J.A. Stankovic. Analysis of the effects of delays on load sharing. *Computers, IEEE Transactions on*, 38(11):1513 –1525, nov 1989.

- [31] Girija J. Narlikar and Guy E. Blelloch. Space-efficient scheduling of nested parallelism. ACM Transactions on Programming Languages and Systems, 21, 1999.

- [32] Daniel Sanchez, Richard M. Yoo, and Christos Kozyrakis. Flexible architectural support for fine-grain scheduling. In *Proceedings of the* fifteenth edition of ASPLOS on Architectural support for programming languages and operating systems, ASPLOS '10, pages 311–322, New York, NY, USA, 2010. ACM.

- [33] Peter Sewell, Susmit Sarkar, Scott Owens, Francesco Zappa Nardelli, and Magnus O. Myreen. x86-tso: a rigorous and usable programmer's model for x86 multiprocessors. *Commun. ACM*, 53:89–97, July 2010.

- [34] Seiji Umatani, Masahiro Yasugi, Tsuneyasu Komiya, and Taiichi Yuasa. Pursuing laziness for efficient implementation of modern multithreaded languages. In *ISHPC*, pages 174–188, 2003.

## A. Experiments

Detailed description of test machine. Our test machine hosts four eight-core Intel Xeon X7550 [23] chips with each core running at 2.0GHz. Each core has 32Kb each of L1 instruction and data cache and 256 Kb of L2 cache. Each chip has an 18Mb L3 cache that is shared by all eight cores. The system has 1Tb of RAM and runs Debian Linux (kernel version 3.2.21.1.amd64-smp). We consider just 30 out of the 32 total cores in order to reduce interference with the operating system. All of our code is compiled by the CilkPlus GCC (v4.8.0 20120625) with the -02 option.

**Thread granularity.** For simplicity, we make the assumption that the granularity of threads is controlled appropriately, so that it suffices to check between every two threads whether the time has come to call the communication functions. (Otherwise, local interrupts can be used, as described in [1].)

*Input data.* The input sizes of the benchmarks are as follows: *cilksort*: random and exponentially-distributed, 240m integers, *matmul*: square matrix of size 3500, *fibonacci*: n = 50, *matching* and *MIS*: 3-d grid with 140m nodes, random graph with 500m nodes and 5b edges, and rMat graph with 500m nodes and 5b edges, *hull*: uniform and plummer with 800m points, *sample-sort*: random and exponentially-distributed, 240m doubles.

In-depth analysis of our results. By comparing with the performance of the Chase-Lev algorithm, and by investigating detailed statistics on the runs, we can identify several causes of the difference in performance of our algorithm with respect to Chase-Lev and Cilk Plus. Tables 8 and 9, and Table 10 show the three key statistics: number of steals, total parallel work, and relative idle time. Total parallel work is measured by summing the running times of all the sequentialized leaves of the call tree. The statistics show that the two algorithms which use concurrent deques achieve a slightly better utilization of the cores by performing quicker steals. However, better utilization does not always pay off because in a few cases there is a corresponding increase in the number of steals, cache misses, and in a few cases CAS conflicts. We see the impact of the cache misses and CAS conflicts by examining the total parallel work measures, which show that, for example for matching(eggrid2d), poorer utilization correlates with less total parallel work. In this case, better utilization of cores effectively slows down the application by creating a bottleneck on the memory. Another cause of their relative poor performance is that the concurrent deques algorithms have to pay for the cost of the fence, which we have measured, when running with a single processor, to represent almost 5% of overhead.

|                       | Our WS       | Our WS   | Chase | PD/CAS |

|-----------------------|--------------|----------|-------|--------|

|                       |              | + Our JP | Lev   |        |

|                       | (nb. steals) | (%)      | (%)   | (%)    |

| matmul                | 2199         | +0.9     | +1.8  | -3.1   |

| cilksort (exptintseq) | 3169         | -13.0    | +2.6  | -1.3   |

| cilksort (randintseq) | 3127         | -9.4     | +4.8  | -7.4   |

| fib                   | 833          | -14.1    | +7.8  | -7.3   |

| matching (eggrid2d)   | 63449        | -25.7    | +15.4 | +2.9   |

| matching (egrlg)      | 74326        | -21.2    | +13.4 | +2.1   |

| matching (egrmat)     | 74118        | -21.5    | +13.3 | +2.5   |

| MIS (grid2d)          | 31328        | -29.5    | +13.9 | +0.4   |

| MIS (rlg)             | 40223        | -27.0    | +13.6 | +3.1   |

| MIS (rmat)            | 40840        | -26.3    | +12.5 | +1.7   |

| hull (plummer2d)      | 8780         | -21.4    | +8.9  | +2.9   |

| hull (uniform2d)      | 10915        | -16.0    | +5.8  | -0.7   |

| sort (exptseq)        | 3852         | -14.1    | +10.5 | +3.3   |

| sort (randdblseq)     | 3953         | -13.4    | +9.1  | -1.8   |

Figure 8. Number of steals.